Tại sao nên sử dụng Xilinx FPGA XC3S500E-4FTG256I?

Nếu là nhà thiết kế kỹ thuật điện tử, bạn có thể biết chip XC3S500E-4FTG256I .

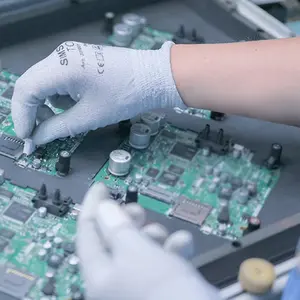

Mảng cổng lập trình trường (FPGA) này được sử dụng rộng rãi trong nhiều ứng dụng khác nhau, từ điện tử tiêu dùng đến điều khiển công nghiệp, hàng không, quân sự và các lĩnh vực khác.

FPGA là một thiết bị bán dẫn bao gồm một ma trận Khối logic có thể định cấu hình (CLB) được kết nối thông qua các kết nối có thể lập trình được. Người dùng xác định các kết nối này bằng cách lập trình SRAM. CLB có thể đơn giản (Cổng AND, OR, v.v.) hoặc phức tạp (một khối RAM). FPGA cho phép thực hiện các thay đổi đối với thiết kế ngay cả sau khi thiết bị được hàn vào PCB.

Trong bài viết này, bạn sẽ tìm hiểu về một số thông tin cơ bản về XC3S500E-4FTG256I của Xilinx, đồng thời khám phá cách sử dụng chuyên nghiệp và các tính năng của nó.

XC3S500E-4FTG256I là gì?

XC3S500E-4FTG256I thuộc dòng Spartan-3E FPGA, được thiết kế bởi Xilinx.

Dòng Spartan-3E cung cấp giải pháp FPGA tiết kiệm chi phí với mức tiêu thụ điện năng thấp, hiệu suất cao và các tính năng cấp hệ thống nâng cao.

Xilinx Zynq FPGA

XC3S500E-4FTG256I có 500.000 cổng hệ thống, 772 I/O người dùng và 36 khối RAM.

Nó hoạt động ở tần số tối đa 400 MHz và có dải điện áp lõi từ 1,14V đến 1,26V.

XC3S500E-4FTG256I thường được sử dụng trong các ứng dụng như hàng không vũ trụ và quốc phòng, ô tô, phát thanh truyền hình, người tiêu dùng, điện toán hiệu năng cao, công nghiệp, y tế và khoa học, thử nghiệm và đo lường.

Yêu cầu Xilinx XC3S500E-4FTG256I FGPA gốc và mới ngay bây giờ

Tính năng của XC3S500E-4FTG256I

• Tín hiệu SelectIO

- Tối đa 633 chân I/O

- Mười tám chuẩn tín hiệu một đầu

- Tám chuẩn tín hiệu vi sai bao gồm LVDS và RSDS

- Hỗ trợ tốc độ dữ liệu kép (DDR)

• Tài nguyên logic

- Các ô logic dồi dào có khả năng đăng ký thay đổi

- Bộ ghép kênh rộng

- Logic mang nhìn về phía trước nhanh

- Bộ nhân 18 x 18 chuyên dụng

- Logic JTAG tương thích với IEEE 1149.1/1532

• Chọn bộ nhớ phân cấp RAM

- Tổng khối RAM lên tới 1.728 Kbit

- Tối đa 432 Kbit trong tổng RAM được phân phối

• Trình quản lý đồng hồ kỹ thuật số (bốn DCM)

- Loại bỏ độ lệch đồng hồ

- Tổng hợp tần số

- Dịch pha có độ phân giải cao

English

English Español

Español Português

Português русский

русский français

français 日本語

日本語 Deutsch

Deutsch Tiếng Việt

Tiếng Việt Italiano

Italiano Nederlands

Nederlands ไทย

ไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা

বাংলা Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türk

Türk Gaeilge

Gaeilge عربى

عربى Indonesia

Indonesia norsk

norsk čeština

čeština Ελληνικά

Ελληνικά Українська

Українська Javanese

Javanese فارسی

فارسی български

български ລາວ

ລາວ Latine

Latine Қазақ

Қазақ Euskal

Euskal Azərbaycan

Azərbaycan slovenský

slovenský Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski Српски

Српски 简体中文

简体中文 繁體中文

繁體中文 Беларус

Беларус